考试科目分为政治理论、外语、数学-和计算机学科专业基础综合四科。还不清楚计算机考研有哪些科目的小伙伴,赶紧来瞧瞧吧!本文整理“计算机组成原理基础知识整理:多模块存储器”相关内容,一起来看。

为了提高访存速度。(CPU速度比存储器快,同时从存储器中取出n条指令,可以充分利用CPU资源,提高运行速度)

(1)单体多字系统

在一个存取周期内,从同一地址取出n条指令,然后逐条将指令送至CPU执行,即每隔1/n存取周期,主存向CPU送一条指令,增大了存储器的带宽,提高了存储器的工作速度。

例如:从同一地址取出4条指令,为单体四字结构,每字W位。按地址在一个存取周期内可读出4*W位的指令或数据,使主存带宽提高到4倍。

缺点:指令和数据在主存内必须是连续存放的,一旦遇到转移指令,或者操作数不能连续存放,这种方法的效果就不明显。

(2)多体并行系统

采用多提模块组成的存储器。每个模块可以并行工作,也可以交叉工作。

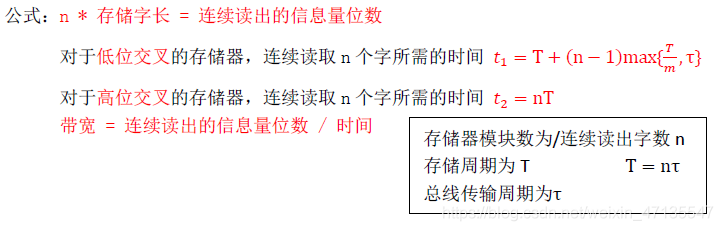

①低位交叉编址

程序连续存放在相邻体中(交叉存储)。低位地址表示体号,高位地址表示体内地址。

地址的低n为片选。

优点:相邻地址单元的数据放在不同组,各组可以并行工作,能较好提高存储器的带宽。

缺点:某一组出现故障,会影响整个存储器的正常工作。

②高位交叉编址

按体内地址顺序存放(顺序存储)。高位地址表示体号,低位地址表示体内地址。

地址的高n位片选。

优点: 某一组的故障不影响其他组,且容易通过添加模块来扩充容量。

缺点:相邻地址单元的数据放在同一组存储单元,各组间串行工作,不利于提升存储器的带宽。